NVL72 全连接域

基本结构

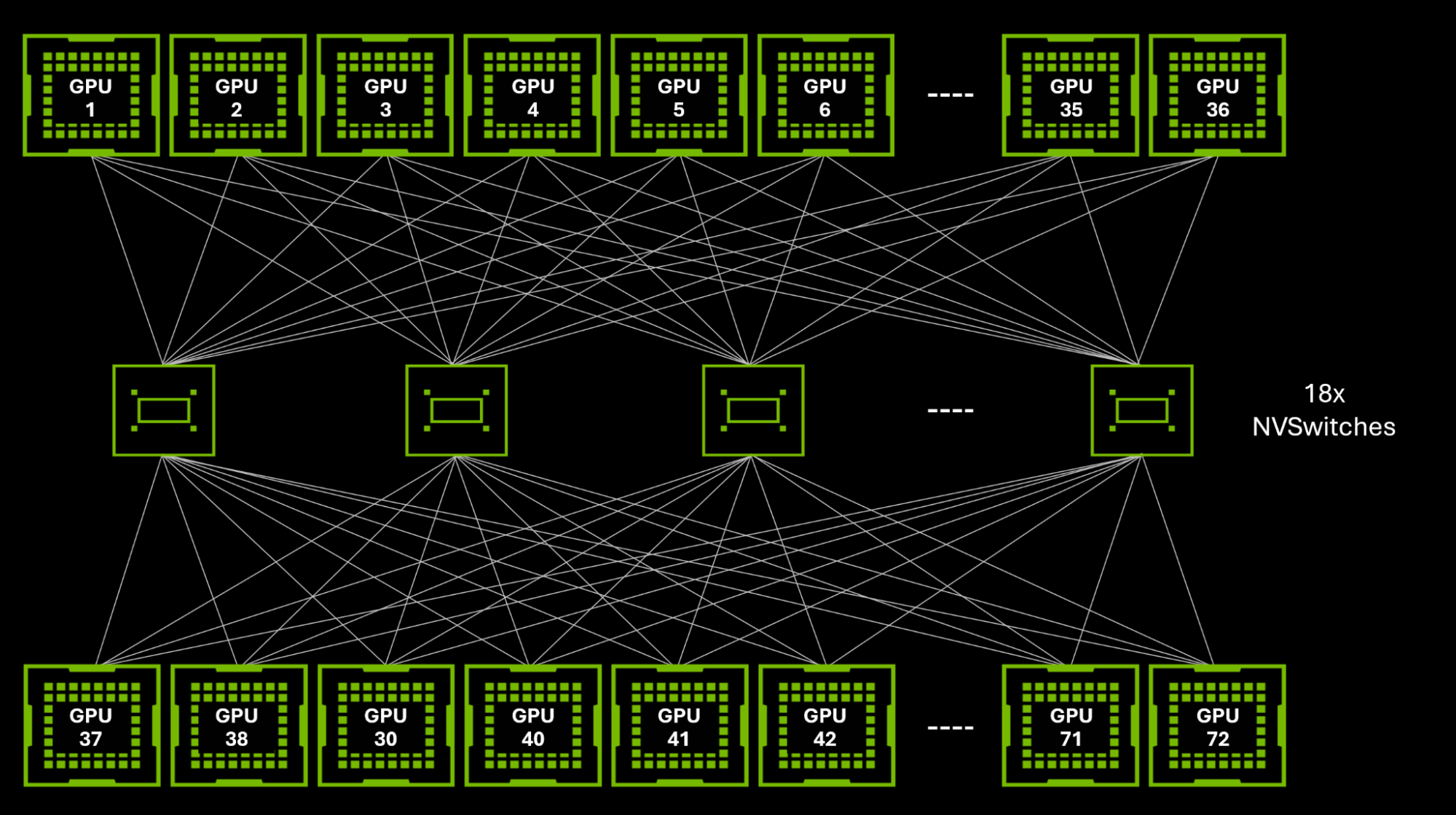

GB200 NVL72 是 NVIDIA Blackwell 架构的关键突破——将 NVSwitch 全互联域从 DGX H100 的 8 GPU 扩展到 72 GPU,整个机架构成一个单一的全互联域。

物理构成(1 个标准机架):

NVL72 机架

├── 18 个 Compute Tray(计算托盘)

│ └── 每个 Tray: 4 颗 B200 GPU (= 2 颗 Grace-Blackwell Superchip)

│ 共 72 颗 B200 GPU

└── 9 个 NVLink Switch Tray(交换托盘)

└── 每个 Tray: 2 颗 NVSwitch 4.0

共 18 颗 NVSwitch 4.0

每颗 B200 GPU 通过 18 条 NVLink 5.0 链路连接到 18 颗 NVSwitch 4.0(每颗 NVSwitch 连接 1 条),由 NVSwitch 在内部完成全交叉交换。逻辑上,任意两颗 GPU 之间可以通过任意 NVSwitch 进行 1 跳通信,实现真正的全互联语义。

关键参数

| 参数 | 值 |

|---|---|

| GPU 数 | 72(36 Grace-Blackwell Superchip,每个含 2 颗 B200) |

| NVSwitch 数 | 18(NVSwitch 4.0,每颗 72 个 NVLink 端口) |

| 每 GPU NVLink 链路数 | 18(NVLink 5.0) |

| 每条 NVLink 5.0 带宽 | 200 GB/s(双向,单向 100 GB/s) |

| 每 GPU NVLink 带宽 | 1,800 GB/s(单向聚合:18 × 100 GB/s;双向 3,600 GB/s) |

| 全域 AllReduce 聚合带宽 | ~260 TB/s |

| 网络直径 | 2 跳(GPU -> NVSwitch -> GPU) |

| 割集带宽 | $\frac{72}{2} \times 1800 \text{ GB/s} = 64.8 \text{ TB/s}$ |

为什么是 72 而非 64 或 128:

- 72 = 36 Superchip × 2 GPUs,受 Grace-Blackwell Superchip 的 D2D 链路和机架物理空间限制

- NVSwitch 4.0 有 72 个 NVLink 端口(相比 3.0 的 64 端口增加 12.5%),18 颗提供 1296 端口,恰好连接 72 GPU × 18 links/GPU

- 128 GPU 需要更多 NVSwitch,功耗和散热超出单 rack 承受能力

通信性能特性

AllReduce

Full Mesh 语义下,Recursive Halving-Doubling 是最优 AllReduce 算法:

$T_{\text{AllReduce}} = 2\lceil \log_2 72 \rceil \cdot \alpha + \frac{2(72-1)}{72} \cdot \frac{M}{\beta}$

- 延迟项:$\alpha$ 为 NVSwitch 交换延迟,实测 <300 ns

- 带宽项:$\beta = 1,800$ GB/s/GPU,AllReduce bus bandwidth 实测 ~839 GB/s(来源:CoreWeave nccl-tests)

AllGather

实测 AllGather bus bandwidth ~1,600 GB/s(来源:CoreWeave nccl-tests)。AllGather 无需 Reduce 操作,带宽利用率更高。

AllToAll

72 GPU 全互联域内,AllToAll 是单跳操作(通过 NVSwitch),理论效率接近 100%。实际受限于每 GPU 18 条 NVLink 链路的并发注入带宽。

与 DGX H100 的对比

| 指标 | DGX H100 | GB200 NVL72 |

|---|---|---|

| 全互联域规模 | 8 GPU | 72 GPU |

| 每 GPU 双向带宽 | 900 GB/s | 1,800 GB/s |

| NVSwitch 代 | 3.0(64 端口) | 4.0(72 端口) |

| 带宽断崖(vs 网络) | 18:1 | 36:1 |

| AllReduce 延迟(1 GB) | 基准 | 更低(带宽 2x) |

适用场景

NVL72 全互联域最适合:

- 大 TP 组:单个 NVL72 可容纳 TP=72 的并行策略,无需跨越带宽断崖

- 超大单体模型:模型参数量超过单 GPU 内存时,在 72 GPU 全互联域内做张量并行,激活层和权重的通信均在高速 NVLink 上完成

- MoE 模型节点内 EP:在 72 GPU 内部分配 Expert,AllToAll 通过 NVSwitch 单跳完成

- 混合精度推理:高频小消息通信在全互联域内零争用完成

局限性

- 带宽断崖 36:1:NVL72 域内 1,800 GB/s vs 对外 InfiniBand 网络 ~50 GB/s(400Gbps)。跨 NVL72 的通信带宽骤降 36 倍,并行策略映射必须严格约束 TP 在 NVL72 内部

- 规模固定为 72:无法灵活配置(不像 Torus 可以调整维度)。72 是由硬件约束决定的固定值

- 成本极高:NVSwitch 4.0 芯片、18 条 NVLink/GPU 的 SerDes 资源,整体系统成本远高于普通 PCIe GPU 服务器

- 功耗与散热:72 GPU + 18 NVSwitch 在单 rack 内,功耗超过 100 kW,需要液冷

- 对外依赖 InfiniBand:NVL72 本身没有跨 rack 的互联能力,需要配合 IB 网络(额外成本)

与华为 CloudMatrix 384 的对比

| 指标 | NVIDIA GB200 NVL72 | 华为 CloudMatrix 384 |

|---|---|---|

| 加速器数 | 72 GPU | 384 NPU |

| 每芯片互联带宽 | 14.4 Tbps(= 1.8 TB/s) | 2.8 Tbps |

| 全互联域规模 | 72 GPU | 384 NPU(L1/L2 两级交换,非物理直连) |

| 互联介质 | 电气 NVLink + 光 NVSwitch 背板 | 全光(400G LPO) |

| 交换架构 | 单级 NVSwitch(18 颗) | L1/L2 两级 UB 交换 |

| 系统 BF16 算力 | 180 PFLOPS | 300 PFLOPS |

| 机架数 | 1 | 16 |

关键差异:NVIDIA 以更高的单芯片带宽(5× UB)换取单机架集成;华为以更大的全互联域规模(5.3× GPU 数量)和全光互联换取跨机架扩展能力。两者代表"带宽密度 vs 规模"的不同工程权衡。

需要注意:CloudMatrix 384 的"全互联域"是通过 L1/L2 两级交换实现的逻辑全互联,跨节点延迟增加 <1 μs,带宽衰减 <3%——并非物理直连全互联。

来源:SemiAnalysis CloudMatrix 384、UB-Mesh arxiv 2503.20377

在大模型集群中的实际应用

NVL72 作为单 rack 全互联域,与集群级 InfiniBand Fat-tree 配合使用:

| 集群 | 规模 | NVL72 数 | 节点间网络 |

|---|---|---|---|

| CoreWeave(首批) | 1,440 B200 | 20 个 NVL72 | IB XDR + SHARP |

集群级拓扑:多个 NVL72 通过 InfiniBand XDR(800 Gbps)互联,组成更大的 Fat-tree 集群。每个 NVL72 是集群的"超节点",内部全互联,对外单个 IB 上行链路。

并行策略映射:

- TP(张量并行):在单 NVL72 内,带宽 1,800 GB/s,TP 组大小可达 72

- PP(流水线并行):跨 NVL72,通过 IB 400Gbps 通信,需要 micro-batch 流水线掩盖延迟

- DP(数据并行):跨 NVL72,每步 DP AllReduce 通过 IB 完成

- EP(专家并行):理想情况是 EP 组在 NVL72 内完成;跨 NVL72 的 EP 需要走 IB,带宽骤降

来源:NVIDIA GB200 NVL72、CoreWeave nccl-tests

参考资料

| 资料 | 关键内容 |

|---|---|

| NVIDIA GB200 NVL72 官方页面 | 72 GPU NVLink 5.0 域规格 |

| NVIDIA Developer Blog, NVL72 OCP | NVL72 NVLink 域拓扑(官方图) |

| CoreWeave nccl-tests | NVL72 AllReduce/AllGather 实测数据 |

| SemiAnalysis CloudMatrix 384 | NVL72 vs CloudMatrix 384 深度对比 |

| arxiv 2506.12708 | CloudMatrix 384 LLM 推理基准 |