NVLink 互联技术

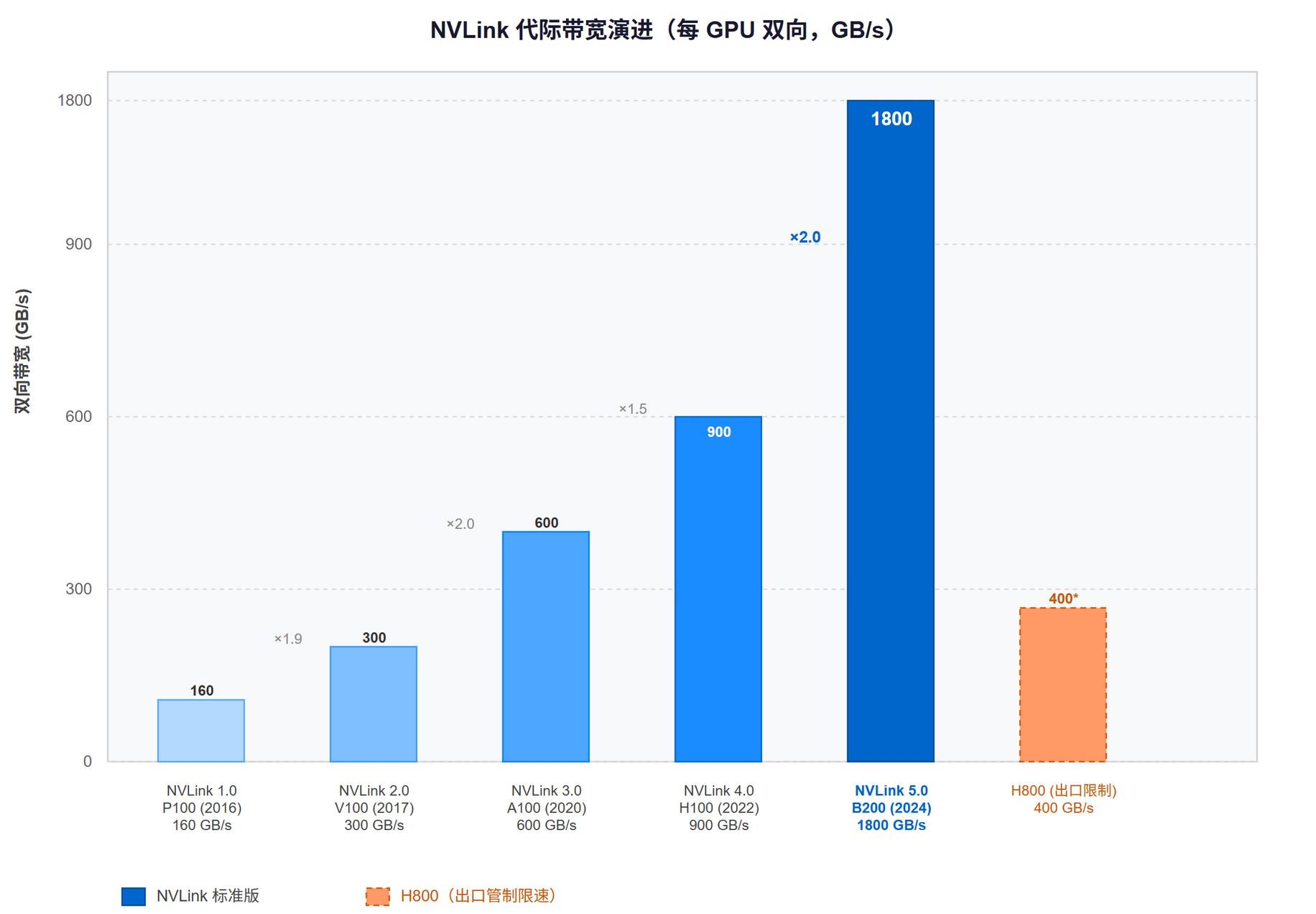

NVIDIA 专有高速芯片间互联协议,自 2016 年 Pascal 架构起逐代迭代,每代带宽大致翻倍,是 NVIDIA GPU 节点内高性能集合通信的物理基础。

代际规格演进

| 代际 | 年份 | GPU 架构 | 信号速率 | 链路数/GPU | 单向带宽 | 双向带宽 |

|---|---|---|---|---|---|---|

| NVLink 1.0 | 2016 | Pascal(P100) | 20 Gbps/lane | 4 | 80 GB/s | 160 GB/s |

| NVLink 2.0 | 2017 | Volta(V100) | 25 Gbps/lane | 6 | 150 GB/s | 300 GB/s |

| NVLink 3.0 | 2020 | Ampere(A100) | 50 Gbps/lane(PAM4) | 12 | 300 GB/s | 600 GB/s |

| NVLink 4.0 | 2022 | Hopper(H100/H200) | 50 Gbps/lane | 18 | 450 GB/s | 900 GB/s |

| NVLink 5.0 | 2024 | Blackwell(B200/GB200) | 100 Gbps/lane(PAM4) | 18 | 900 GB/s | 1800 GB/s |

H800 是 H100 的中国出口版本,NVLink 带宽被限制到 400 GB/s 双向(NVLink 4.0 链路数削减)。

从 P100 到 B200,8 年间带宽增长约 11 倍。NVLink 3.0 引入 PAM4 调制将信号速率翻倍;NVLink 5.0 再次将信号速率翻倍到 100 Gbps/lane。

Flit 协议结构

NVLink 使用 flit(Flow Control Unit) 作为基本传输单元。

- 每个 flit:128-bit(16 bytes)

- Header flit 结构:25-bit CRC + 83-bit 事务层 + 20-bit 数据链路层(DL layer)

- 数据包结构:1 个 header flit + 可选 AE/BE flit + 最多 16 个 data payload flit

最大 payload 为 16 × 16B = 256B。每个数据包必须携带 1 个 header flit,构成固定开销。

来源:WikiChip (https://en.wikichip.org/wiki/nvidia/nvlink)

带宽效率实测

协议效率 = Payload Flit 数 / 总 Flit 数,反映 header 开销占比。

| Payload 大小 | Header Flit | Payload Flit 数 | 总 Flit 数 | 单向效率 | 双向效率 |

|---|---|---|---|---|---|

| 256B | 1 (16B) | 16 | 17 | 94.1% | 88.9% |

| 128B | 1 (16B) | 8 | 9 | 88.9% | ~80% |

| 64B | 1 (16B) | 4 | 5 | 80.0% | 66.7% |

| 32B | 1 (16B) | 2 | 3 | 66.7% | ~57% |

| 16B | 1 (16B) | 1 | 2 | 50.0% | ~40% |

结论:对于 NCCL 集合通信(通常使用 256 KB+ 的 chunk,每次传输大量 256B 最大 flit),协议开销可忽略(>94% 效率)。小消息场景(<32B)效率骤降到 50% 以下,但此时软件栈启动延迟才是主导因素。

软件层开销

NVLink 物理层效率高,但软件层引入了不可忽视的延迟:

- NCCL 启动延迟:约 20-60 us,与消息大小无关。这是 NCCL 内核 launch、同步开销。

- 小消息行为:消息 <256 KB 时,NCCL 启动延迟主导,实测 AlgBW 远低于线速。

- 大消息行为:消息 >4 MB 时,带宽逐渐饱和,接近线速利用率 90-95%。

- NVLS 启用阈值:NCCL 2.17+ 在消息 >256 KB 时自动检测并启用 NVLS,进一步提升 AllReduce 效率。

NVSwitch 架构

NVSwitch 是配合 NVLink 使用的专用互联交换芯片,实现同一节点内所有 GPU 的全连接(Full Mesh)。NVSwitch 的引入使 NVLink 域从 GPU-to-GPU 直连扩展到 All-to-All 无阻塞交叉互联。

从 Gen3(Hopper)起,NVSwitch 内置了计算引擎,支持 NVLS(NVLink SHARP)网内计算。

详细内容见 nvswitch-nvls.md。