互联硬件技术总览

本文从横向视角梳理 AI 芯片互联技术的分类、代际演进与在大模型集群中的分层角色,作为后续各专题文档的导航入口。

名词定义

| 名词 | 定义 |

|---|---|

| 节点内互联(Intra-node Interconnect) | 同一服务器或机箱内芯片之间的直接互联,带宽通常为数百 GB/s,代表技术有 NVLink、xGMI、ICI、HCCS |

| 节点间网络(Inter-node Network) | 跨服务器的网络互联,带宽通常为数十 GB/s,代表技术有 InfiniBand、RoCEv2 |

| 双向带宽(Bidirectional Bandwidth) | 链路同时收发的聚合带宽,等于单向带宽的两倍,NVLink 通常以此口径报告 |

| 单端口线速(Port Line Rate) | 交换机或网卡单个物理端口在全速状态下的数据传输速率,节点间网络以此口径报告 |

| RDMA(Remote Direct Memory Access) | 绕过 CPU 直接在两台机器内存间传输数据的技术,显著降低延迟和 CPU 占用,InfiniBand 和 RoCEv2 均基于此 |

| Flit(Flow Control Unit) | 链路层流量控制的最小单元,一个数据包由多个 flit 组成,flit 大小决定协议效率 |

| 协议效率(Protocol Efficiency) | 有效载荷占总传输数据(含协议头)的比例,消息越小效率越低 |

| BusBW(Bus Bandwidth) | nccl-tests 报告的总线带宽,按 Ring 算法流量因子 $2(N-1)/N$ 折算,便于跨规模比较 |

| 片内互联(Die-to-Die Interconnect) | 同一芯片封装内多个裸片之间的互联,带宽为 TB/s 级,对用户透明,代表技术有 AMD xGMI(MI300X 内部)、SG2262 D2D |

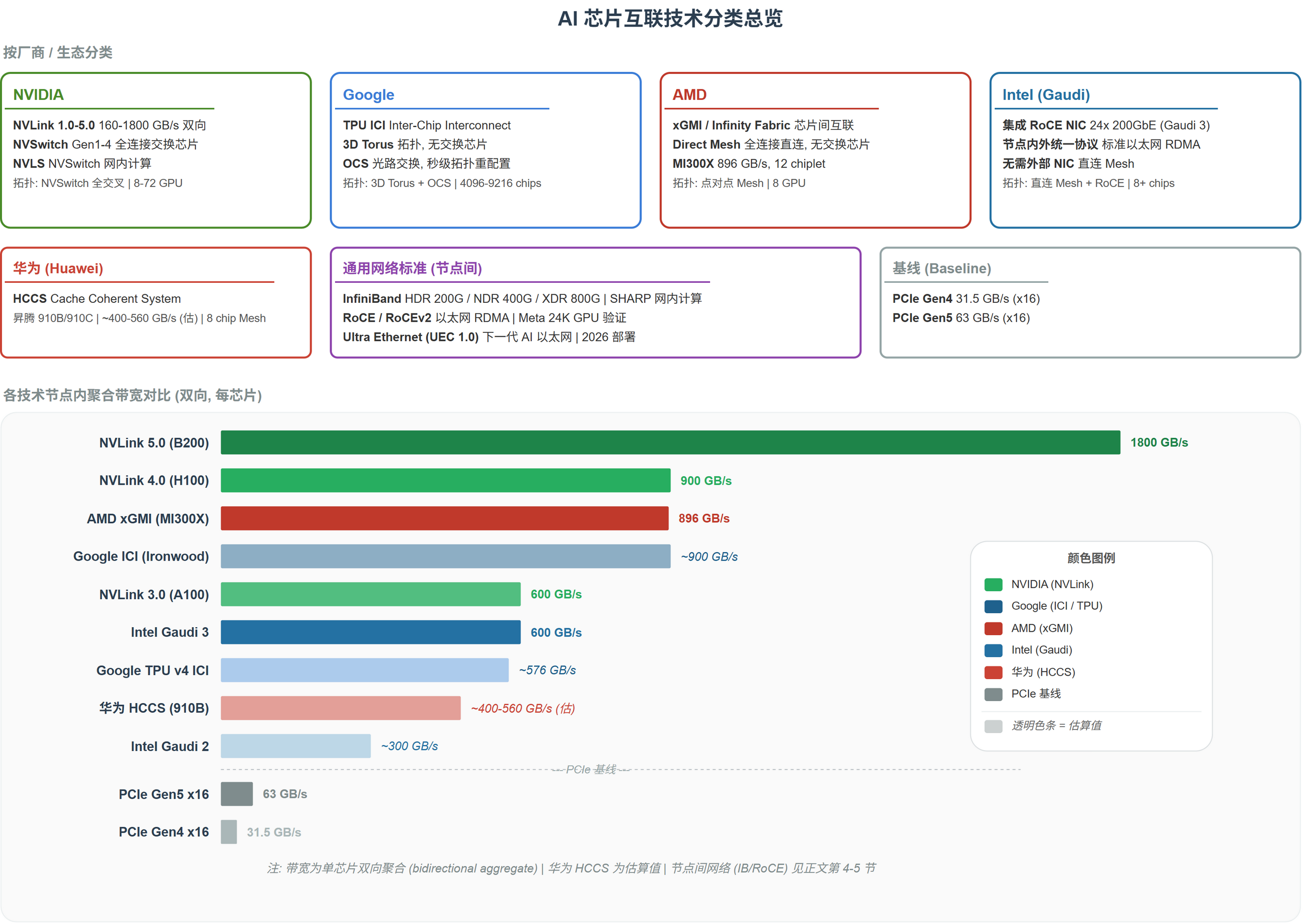

主要互联技术对比

节点内互联和节点间网络属于不同层级,带宽口径不同,不可直接横比。

节点内互联(同一服务器/机箱内,每芯片聚合双向带宽)

| 技术 | 厂商 | 适用层级 | 带宽范围(双向,每芯片) | 代表产品 |

|---|---|---|---|---|

| NVLink 5.0 | NVIDIA | 节点内 | 1800 GB/s | B200 / GB200 NVL72 |

| NVLink 4.0 | NVIDIA | 节点内 | 900 GB/s | H100 / H200 |

| NVLink 3.0 | NVIDIA | 节点内 | 600 GB/s | A100 |

| xGMI / Infinity Fabric | AMD | 节点内 | 896 GB/s | MI300X |

| ICI (Ironwood/TPU7x) | 节点内+跨机架 | ~1200 GB/s | TPU7x | |

| ICI (TPU v4) | 节点内+跨机架 | ~576 GB/s | TPU v4 | |

| Gaudi 3 RoCE | Intel | 节点内+跨节点 | 600 GB/s | Gaudi 3 |

| HCCS (910B) | 华为 | 节点内 | ~400-560 GB/s(估) | 昇腾 910B |

| PCIe Gen5 x16 | 通用 | CPU-加速卡 | 126 GB/s | 基线参考 |

| PCIe Gen4 x16 | 通用 | CPU-加速卡 | 63 GB/s | 基线参考 |

节点间网络(跨服务器,单端口线速)

| 技术 | 适用层级 | 单端口带宽 | 延迟 | 代表部署 |

|---|---|---|---|---|

| InfiniBand XDR | 节点间 | 800 Gbps (~100 GB/s) | ~1-2 us | DGX B200 |

| InfiniBand NDR | 节点间 | 400 Gbps (~50 GB/s) | ~1-2 us | DGX H100 |

| InfiniBand HDR | 节点间 | 200 Gbps (~25 GB/s) | ~1-2 us | DGX A100 |

| RoCEv2 (400GbE) | 节点间 | 400 Gbps (~50 GB/s) | ~2-5 us | Meta 24K GPU 集群 |

代际演进时间线

NVLink 代际带宽演进(每 GPU 双向)

| 年份 | 代际 | GPU | 双向带宽 | 增幅 |

|---|---|---|---|---|

| 2016 | NVLink 1.0 | P100 | 160 GB/s | 基线 |

| 2017 | NVLink 2.0 | V100 | 300 GB/s | 1.9x |

| 2020 | NVLink 3.0 | A100 | 600 GB/s | 2.0x |

| 2022 | NVLink 4.0 | H100 / H200 | 900 GB/s | 1.5x |

| 2024 | NVLink 5.0 | B200 / GB200 | 1800 GB/s | 2.0x |

8 年间 NVLink 带宽增长约 11 倍,每代大致翻倍。

InfiniBand 代际演进

| 年份 | 代际 | 每端口线速 | 典型部署 |

|---|---|---|---|

| 2019 | HDR | 200 Gbps | DGX A100 |

| 2022 | NDR | 400 Gbps | DGX H100 |

| 2025 | XDR | 800 Gbps | DGX B200 |

| ~2027 | GDR(预期) | 1.6 Tbps | 下一代 |

Google TPU ICI 演进

| 年份 | 代际 | 每芯片 ICI 带宽 | 拓扑 | Pod 规模 |

|---|---|---|---|---|

| 2017 | TPU v2 | ~500 Gbps (4 链路) | 2D Torus | 256 chips |

| 2018 | TPU v3 | ~656 Gbps (6 链路) | 2D Torus | 1024 chips |

| 2022 | TPU v4 | ~4.8 Tbps (6 链路) | 3D Torus | 4096 chips |

| 2023 | TPU v5p | ~4.8 Tbps | 3D Torus | 8960 chips |

| 2025 | Ironwood (TPU7x) | ~9.6 Tbps (1200 GB/s) | 3D mesh(direct-neighbor) | 9216 chips |

PCIe 代际演进

| 代际 | 单向带宽 (x16) | 双向带宽 | 典型场景 |

|---|---|---|---|

| PCIe Gen3 x16 | 15.75 GB/s | 31.5 GB/s | 旧 GPU(V100 PCIe) |

| PCIe Gen4 x16 | 31.5 GB/s | 63 GB/s | A100 PCIe、H20 |

| PCIe Gen5 x16 | 63 GB/s | 126 GB/s | H100 PCIe、B200 PCIe |

| PCIe Gen6 x16 | ~128 GB/s | ~256 GB/s | 下一代(待商用) |

在大模型集群中的角色

大模型系统的互联需求按物理层级划分,各层性能差异决定了哪种并行策略最优:

层级 1: 片内互联(Die-to-Die)

带宽: TB/s 级 | 延迟: ns 级

例: AMD MI300X chiplet 间 xGMI,SG2262 Die-to-Die

角色: 单芯片内的裸片间数据搬运,对用户透明

层级 2: 节点内互联(Chip-to-Chip,同一服务器)

带宽: 数百 GB/s | 延迟: 1-2 us

例: NVLink 4.0/5.0,xGMI,ICI,HCCS,PAXI

角色: Tensor Parallelism(TP)的主要通信层;AllReduce 延迟敏感

层级 3: 机架内跨节点(Node-to-Node,同 Rack)

带宽: 数十 GB/s | 延迟: 2-5 us

例: InfiniBand NDR/XDR,RoCEv2

角色: Pipeline Parallelism(PP)的 P2P 通信;Data Parallelism(DP)梯度同步

层级 4: 跨机架/跨 Pod(Rack-to-Rack,Pod-to-Pod)

带宽: 数十 GB/s(受交换机瓶颈) | 延迟: 5-20 us

例: IB Fat-tree,RoCE Spine

角色: Expert Parallelism(EP)的 AllToAll;大规模 DP 梯度同步

关键洞察:同一 GPU 在不同互联条件下,集合通信性能可以相差 10 倍以上。选择正确的并行策略,核心是尽量让通信量大的操作(TP AllReduce)落在带宽最高的层级(节点内互联)。

关键性能指标

| 指标 | 定义 | 测量工具 | 说明 |

|---|---|---|---|

| BusBW | AlgBW × 2(N-1)/N,nccl-tests 报告的总线带宽 | nccl-tests | 按 Ring 算法流量因子折算,便于跨规模比较 |

| AlgBW | MessageSize / Time,不含流量因子的原始算法带宽 | nccl-tests | 反映实际端到端吞吐 |

| 线速利用率 | AlgBW / 物理线速 | 计算 | 衡量协议和软件效率;NVLink 大消息可达 93-106% |

| 单跳延迟 | 单次数据包从发送到接收的时间 | ping/RDMA lat test | NVLink: ~1-2 us;IB NDR: ~1-2 us;RoCE: ~2-5 us |

| 协议效率 | Payload / (Payload + Header) | 分析 flit 结构 | NVLink 256B payload: 94.1%;小消息下显著下降 |

文档导航

| 文档 | 内容 |

|---|---|

| 01-nvlink.md | NVLink 协议规格、Flit 结构、带宽效率 |

| 02-nvswitch-nvls.md | NVSwitch 交换架构、NVLS 网内计算 |

| 03-infiniband.md | InfiniBand HDR/NDR/XDR 规格、RDMA 传输 |

| 04-roce.md | RoCE v1/v2 协议栈、拥塞控制 |

| 05-pcie.md | PCIe 代际规格、基线角色 |

| 06-amd-xgmi.md | AMD xGMI/Infinity Fabric、MI300X 互联 |

| 07-google-ici.md | Google TPU ICI、Torus/Mesh 拓扑 |

| 08-国产互联.md | HCCS、PAXI、SG2262 C2C 等国产技术 |

详细的性能建模方法见 06-通信性能建模。